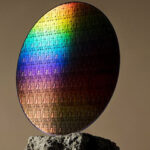

La course ininterrompue à la miniaturisation impose la recherche d’architectures toujours plus performantes et moins gourmandes en énergie pour les composants électroniques. Mais jusqu’où pourrait aller le développement des transistors ? La loi de Moore est-elle encore viable ? Formulée en 1965 par Gordon Moore, cofondateur d’Intel, cette règle empirique stipule que les semi-conducteurs aboutissent (pour un prix de revient constant), tous les dix-huit mois, à un doublement du nombre de transistors présents sur une même surface de circuit. « Cette loi s’est longtemps vérifiée mais elle a changé de nature depuis quelques années », constate Thomas Ernst, le directeur scientifique du CEA-Leti. « Un processeur comme celui qui équipe notre téléphone portable contient des milliards de transistors connectés les uns aux autres sur une surface de moins d’un centimètre carré. Il fonctionnera d’autant plus vite et consommera d’autant moins d’énergie que ses composants seront plus petits et rapprochés les uns des autres, permettant au courant de passer avec une rapidité croissante. »

Résultat : les industriels améliorent continuellement la finesse de gravure des circuits et miniaturisent les transistors pour pouvoir insérer plus dans un même espace. « Jusqu’en 2012, ces derniers progressaient au rythme de la loi de Moore », explique l’expert du CEA. « Ils parvenaient ainsi à diminuer les dimensions de ces éléments de 1,4 fois par an. Aujourd’hui c’est fini, car l’augmentation des coûts due à la mise en œuvre de procédés de fabrication toujours plus longs et complexes, ainsi que la baisse des rendements provoquée par le passage à des technologies supportant de moins en moins les défauts, ont ralenti le rythme avec lequel les générations de semi-conducteurs se succèdent. ». La technologie commence à se heurter à des limites de nature physique. Pourquoi ? « En dessous d’une certaine taille, “l’effet tunnel” à la base du fonctionnement du transistor n’est plus maîtrisable. Ce qui provoque des fuites de courant incontrôlées et échauffent les puces », répond Denis Dutoit, ingénieur-chercheur au CEA-List.

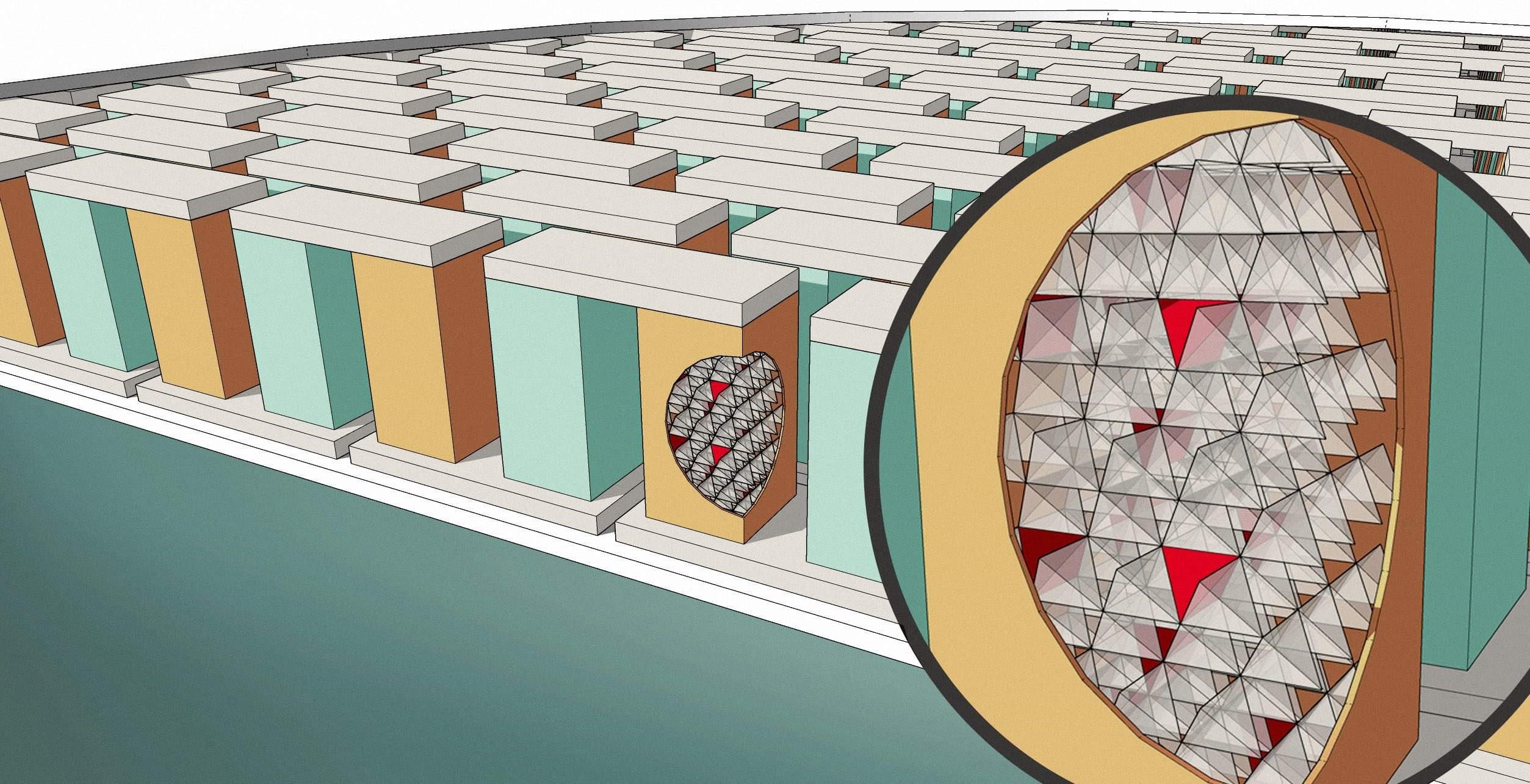

Alors, pour espérer franchir le nœud technologique des 2 nm, TSMC, Intel et autre Samsung n’auront d’autres solutions que de recourir à la technologie des nanorubans et à des nouvelles techniques d’intégration 3D. Demain on pourra peut-être réussir à produire des puces 3D dans lesquelles les transistors ne seraient plus répartis sur la surface d’une plaquette de silicium mais superposés les uns sur les autres sur plusieurs niveaux pour gagner de la place. Une technologie encore au stade de prototypes. Ainsi, de nouveaux transistors développés par IBM et Samsung et baptisés VTFET (photo, source : IBM) ne sont pas disposés à plat comme c’est le cas à l’heure actuelle, mais verticalement. Une conformation spatiale qui apporte selon leurs concepteurs une hausse de la densité logique, un doublement des performances et une baisse de 85% de la consommation énergétique. Cependant, il ne faut pas oublier d’autres défis, comme la limitation de la quantité de matières premières nécessaires et la mise en œuvre des méthodes de recyclage.

Sur le même sujet

octobre 2024

© Yoan Jeudy pour Micronora Le salon Micronora, qui s’est tenu du 24 au 27 septembre 2024, à Besançon (France), a confirmé une fois de plus sa place de leader [...]

septembre 2023

La première micro-machine européenne date de 2016 : sept ans plus tard, plusieurs entreprises et écoles proposent des modèles innovants : La nouvelle création d’ENOVEAS représente une avancée décisive pour [...]

août 2023

Au cœur des générateurs thermoélectriques, des matériaux semi-conducteurs sont intensivement étudiés pour accroître les performances de ces dispositifs qui génèrent de l’électricité à partir de chaleur. Des chimistes du Laboratoire [...]